|

|

Implementation of the NOR gate from the NAND gate is possible because NAND is a Universal gate i.e., it can implement all other gates. The NAND gate gives output low when all the inputs are high whereas the NOR gate gives output high when all inputs are low. In this article, we will implement the NOR gate using the NAND gate. Table of Content What is NOR Gate?NOR gate is a logic gate that gives output 1 when all the inputs are 0. In other words, the output is high when all inputs are low. NOR gate is a Universal gate. It is the complement of the OR gate. 2-Input NOR GateThe NOR gate with 2 inputs is called a 2-input NOR gate. It gives the output high when both the inputs are low. The truth table for 2-Input NOR GateThe following truth table represents the NOR gate.

Expression for 2-Input NOR GateFrom the above truth table, expression for NOR gate is:

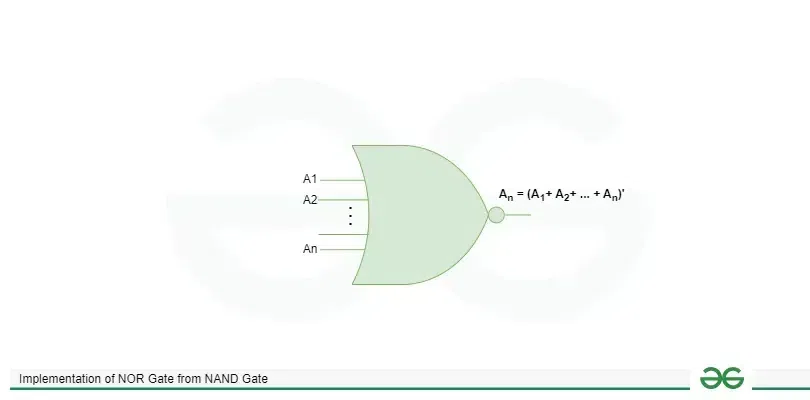

Logic Diagram of 2- Input NOR GateBelow is the logic diagram for NOR gate.  Logic Diagram for NOR Gate n-Input NOR GateThe NOR gate with n-inputs is called as n-input NOR gate. It gives the output high when all the inputs are low otherwise output is low. In other words, the output is low when any one of the inputs among n inputs is high. Expression for n-Input NOR GateIf the inputs are A1, A2, …, An then,

Logic Diagram for n-Input NOR GateBelow is the logic diagram for n-input NOR gate.  n-Input NOR Gate What is NAND Gate?NAND gate is a logic gate which gives output 0 when all the inputs are 1. In other words, the output is low when all inputs are high. It gives output high if at least one input is low. NAND gate is a Universal gate. It is the complement of AND gate. 2-Input NAND GateA 2-input NAND gate is a logic gate which gives output high when at least one input is low. It gives low output when both the inputs are high. Truth Table for 2- Input NAND GateThe following truth table represents the NAND gate.

Expression for 2-Input NAND GateFrom the above truth table expression for NAND gate is: A NAND B = A’B’ + A’B + AB’

Logic Diagram of 2- Input NAND GateBelow is the logic diagram of NAND gate.  NAND Gate Logic Diagram n-Input NAND GateThe NAND gate with n inputs is called n-input NAND gate. In this logic gate the output is low when all the inputs are high otherwise the output is high. Expression for n-Input NAND GateIf the inputs are A1, A2, …, An then,

Logic Diagram for n-Input NAND GateBelow is the logic diagram for n-input NAND gate.  n-Input NAND Implementation of NOR Gate from NAND GateFollowing is the implementation of NOR gate from NAND gate. First, we produce complements of inputs and further implement NOR logic. Logic Diagram for Implementation of NOR Gate from NAND GateBelow is the logic diagram for the implementation of NOR gate from NAND gate.  Implementation of NOR Gate from NAND Gate

So,This is How the NAND gate can be Implemented as NOR gate. ConclusionFrom the above discussion we can conclude that to implement NOR gate from NAND gate we require 4 NAND gates. First two gates give us the complement of the inputs and then, we connect two more NAND gates to get NOR gate. We also use DE Morgan’s law to convert and of individual complements to whole complement of OR of inputs. FAQs on Implementation of NOR Gate from NAND GateWhat is NAND Gate?

What are Universal Gates?

How Many Gates are Required to Implement NOR Gate from NAND Gate?

What is the Expression for the NOR Gate?

|

Reffered: https://www.geeksforgeeks.org

| Analog And Digital Electronics |

Type: | Geek |

Category: | Coding |

Sub Category: | Tutorial |

Uploaded by: | Admin |

Views: | 11 |